Prev

Next

Prev

Next Site Map

Site Map

Home

Home

| . | . | . | . | David McCracken |

Stepper Motor Circuit Breakerupdated:2017.05.28 |

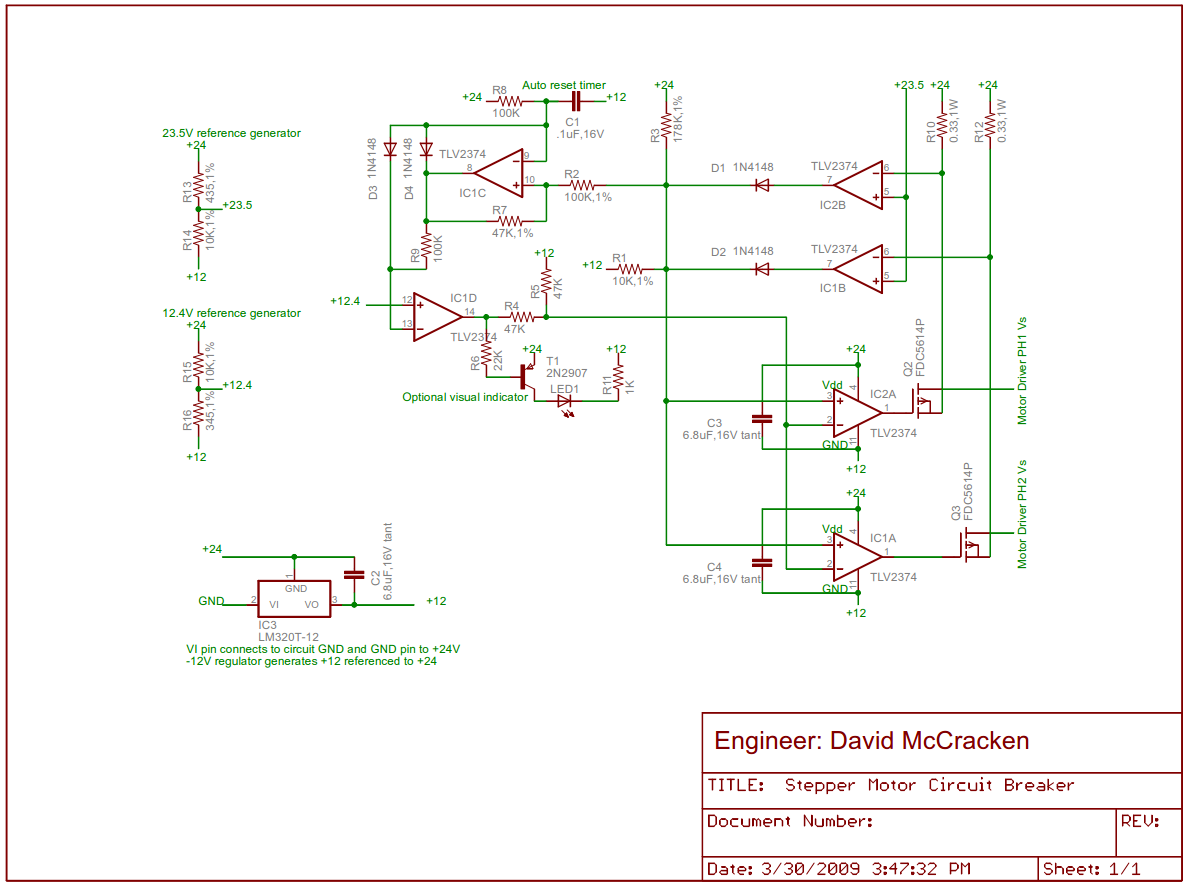

Most full-bridge motor driver circuits, like the TEA3717/18 (STMicroelectronics and others) are automatically protected against low-side short-circuit by their normal PWM current control function. However, many of these components afford no protection at all against a high-side short-circuit, and the protection provided by PWM action is not ideal because the driver may heat up to the point where failure occurs due to secondary breakdown (if bipolar like TEA3717/18) or its longevity is reduced due to thermal stress.

A fast-acting high-side breaker protects the driver in the event that either of its outputs is shorted to ground. It also affords better protection than the driver's built-in PWM current limiting when the terminals are shorted together. It does not protect against shorting one of the output terminals to high voltage but this does not commonly occur and, if it does, at least the driver will have the protection of its own PWM action.

Especially with a stepper motor, if motor power is disrupted for any reason the motor is unlikely to achieve the position expected by the application. In most cases this means that at least a system reboot will be needed. Often a short-circuit condition is temporary, caused, for example, by a conductive fluid spill or a technician's mistake. Ideally, the circuit breaker automatically resets itself to simplify resuming normal operation. If the breaker encounters a continuing short-circuit when it resets, it should immediately turn off the power again. In this situation, the breaker is, in effect, a PWM current limiter. If the duty cycle is very low, no heat will be generated in any components and the condition can continue indefinitely without adverse consequences. This not only affords the motor driver component good protection, but also allows the breaker itself to use very small power components. The Fairchild FDC5614P P-channel MOSFETS used in this design have very little heat dissipation capability yet are safely driven by TI TLV2374 op amps that, while providing good output sourcing and sinking, are not the best components for driving the high-capacitance gate loads of a power MOSFET.

The current from the driver's motor power supply is converted to voltage by a small value (e.g. .1 to .5 ohm) sense resistor. This voltage is compared to a reference. When the current exceeds the maximum threshold, the power to the driver is cut off by switching off a high-side transistor (load switch) and simultaneously triggering a one-shot that prevents the transistor from being turned back on until after a relatively long delay. The long timeout yields a very low duty cycle under shorted conditions so that the load switch and motor driver experience little or no heating.

The entire circuit is referenced to the motor supply high voltage, +24V. Except during turn on/off transitions, the load switch operates fully on or off, dissipating only the power dictated by its efficiency when fully on. When off, it sees 24V; when on nearly 0. A P-channel MOSFET is appropriate for this. The Fairchild FDC5614P has been selected. Its maximum voltage and current are 60V and 3A while its power dissipation is 1.6W when properly mounted on a heat spreading pad (the part itself is a very tiny "SuperSOT") and .8W in air. Its Rdson is 0.1 ohm at Vgs = -10V and 0.135 ohm at Vgs = -4.5V. At 2.5A, its power dissipation is .625W (with Vgs >= -10V). This would be the cutoff level for an A3977 at a 2A maximum set by PWM. Thus, even with no heat spreader, the transistor can handle our maximum current requirement.

Except for the load switch, the rest of the circuit does not need to see ground. We want at least -10V relative to +24 for Vgs. Since we already have +12 power, this might serve as the low voltage (i.e. ground) of the circuit. However, because of competing uses for node voltages in the circuit, some margins are rather small and it would be better not to depend on the main 12V power to provide a consistent voltage relative to 24V. To achieve the greatest possible consistency, the 12V should be referenced not to ground but to the 24V power itself. This can be done with a -12V three-terminal linear regulator such as LM7912 or LM320-12. An unusual connection is used: +24 is connected to the regulator's GND input and analog/power ground to the regulator's IN input. The regulator's OUT terminal sources -12V relative to the +24V rail.

As a MOSFET, the load switch gate presents essentially no DC load and can potentially be driven directly by some op amps. However, there are two problems. One is that the FDC5614P begins to turn on at Vgs = -1V (worst case minimum). When turned off, no current flows through Rsense so the transistor's Source will be at 24V. An op amp driving the gate must pull up to less than 1V from the positive rail to prevent current flow during cutoff. The other problem is that the op amp must source and sink a sizeable current to quickly charge and discharge the large 760 pF gate capacitance to drive the transistor rapidly through its linear range while turning on and off. Additionally, to keep the sense resistor's power dissipation low, the sense voltage is .5V. Since this feeds directly to one input of an op amp, the op amp must work with inputs near the positive rail. To reduce cost, size, and components it is better to use one device for both the overcurrent voltage comparator and the MOSFET driver, although different devices could be used if necessary. This circuit comprises two comparators. Actual comparators could be used but none meet the combination of rail-to-rail input and output, high current output, and supply voltage greater than 12V. An inexpensive quad op amp TLV2374 (Texas Instruments) provides the following characteristics:

The 2374 does not meet all of these characteristics under all conditions. For example, the output voltages are much further from the rails while sourcing or sinking 100mA. However, the Vout-high doesn't need to be near the rail (+24V) until the transistor is already nearly turned off. It means nothing that the output voltage pulls away from the rail while the op amp is sucking 100mA off the gate. The rather slow slew rate is insignificant compared to the gate charging time.

Each of the two motor windings requires a circuit breaker. Since the TLV2374 contains four amplifiers and each circuit requires only two, one TLV2374 could support one motor. However, one possible failure situation is the shorting of both windings simultaneously, for example as might occur if a motor became very hot and fried both its windings. In this situation, both load switches might have to be turned off and on simultaneously (depending on coincidental synchronization of the two one-shots). The 2374 can't source/sink 100mA from two outputs simultaneously. Since it is very unlikely that two motors will simultaneously short, two motor drivers can share two TLV2374s, with one amplifier from each driving the load switch for one motor's winding and another amplifier driving the load switch for a winding of the other motor.

Amplifiers 2B and 1B detect overcurrent in each of the two drivers (one for each winding) of one motor. The trigger current is set by a fixed 23.5V reference on each amplifier's non-inverting input compared to a Vsense caused by the drop across an Rsense. For example, if Rsense is .25 ohm, the trigger point is 2A. When the load current is less than the trigger, the amplifier's output is low (12V). When the current is above the trigger point, the output goes high. The outputs of 2B and 1B are wired-OR using diodes. If either amplifier output goes high, the summing point goes to 23.3V.

Amplifiers 2A and 1A each drive the gate of one of the load switches. They perform identically and synchronously. Two amplifiers are used instead of one only to increase the gate charging current. When the amplifier output is high, the load switch is turned off.

If either 2B or 1B registers an overcurrent both drivers will be rapidly turned off. After a delay, both drivers will be turned back on to try again. The cycle will repeat as long as either driver experiences overcurrent.

All nodes except the overcurrent comparators' OR node have more than enough design margin in all states. The OR node serves both to trigger 1C (out high) and to force 2A and 1A out high in the overcurrent condition. The tricky condition is when there isn't overcurrent so that 2B and 1B outputs are both low. In this state they contribute nothing to the node voltage. This condition occurs at two times: the normal steady state and during the off time initially triggered by overcurrent. In the steady state condition, 1C is the problem. Its In+ voltage must be lower than the 12.7V of the fully discharged (by 1C out through the discharge diode) timing capacitor so that 1C out will remain low. In the timed off state, 2A and 1A are the problem. Their outputs must remain high even though the overcurrent no longer exists. They are held high by In+ being higher than In-, which is driven by 1D out low. Since 1D out can't be lower than 12V, In+ must be greater than 12V.

The OR node low voltage is determined by a resistor that pulls up to 24V, one that pulls down to 12V and 1C out through the feedback and In+ resistors. In the steady state case, 1C out is low. In the temporary off state, 1C is high when the OR node goes low but then goes low when the timing capacitor reaches the 1C In+ voltage (which due to positive feedback is relatively high even when the node voltage returns low). Thus, for 1C the node low voltage only needs to be designed for the case of 1C out low; but for 2A/1A In+ it must be designed for 1C out both high and low. Here, 1C low is the problem case, as we are trying to keep 2A/1A In+ higher than In-. Since 1C low is the only case of interest for 1C In+ as well as the worst case for 2A/1A In+, we can design for it.

1C Rf and In+ are 47K and 100K. Or node V12R is 10K. V24R is selected as 178K for V24R. The Thevenin equivalents of V12R and V24R are 9.47K and 12.64V. With 1C out low, 1C In+ is at 12.19V giving a margin of 0.51V (relative to 0.7V); 2A/1A In+ is at 12.6V giving a margin of 0.5 (if 1D out pulls down to 0.1V). These margins are adequate, but they could be increased by adding another diode in series with the discharge diode (or using an LED, which has 1.4Vf) increasing the 1C In- minimum voltage, which In+ low must match.

1C out and Vcap are summed at 1D In-. 1D In+ voltage is established so that 1D out goes high only when both 1C out is low and the timing capacitor is fully discharged. As already explained, it is important that Vcap not go so low that 1C In+ low can't go lower. The discharge diode ensures a minimum voltage of 0.7V. To prevent 1C out low from reducing Vcap lower than this through the summing resistors, the Vcap summing resistor net contains a diode. Vcap would never reach 0V even without this diode because of the timing resistor to 24V but we don't want to reduce the margin between 1C In- low and 1C In+ low by any amount.

The off time is established by the time it takes Vcap to charge up to the 1C In+ voltage with 1C out high plus the time required to discharge back down to 0.7V. When the overcurrent exists, the OR node voltage will be 23.3V and 1C In+ 15.6V. This causes 1C out to go high, raising 1C In+ to 23.78V. Assuming that Vcap rises much more slowly than the power switches are shut off, OR node voltage will drop back to 20.59V resulting from 1C out 24V through 47K and 12.64V (Thevenin equivalent of V12R and V24R) through 109.47K (100K plus Thevenin R). Therefore, the charging time will be determined by this threshold. Because 1C out is 24V, the summing diode is reverse biased so there is no current flow other than from the timing resistor into the capacitor. The 20.59V threshold is nearly 85% of 24V, which is reached in time = 2*RC. A long power off time is used to reduce the duty cycle of the power elements to a negligible level. However, if the resistor's value is too high, its effectiveness in the 1D In- summing junction is reduced. Therefore, R is 100K and C is .1uF, yielding a charge time of 20 msec. With overload, we should measure approximately 50Hz at 1C out. A test circuit exhibited a frequency of 70Hz.

1C out and Vcap are summed for 1D In-. As already explained, the Vcap leg contains a diode to maintain a minimum 1C In- of .7V. Only the 1C out leg has a resistor, 100K even though this is a summing node. The reason that no resistor is need in the Vcap leg is that the only voltage source, 24V, is already supplied through the timing resistor. When 1C out is high, both the discharge and the summing diodes are reverse biased and 1C out high alone keeps 1D out low. When Vcap reaches the 20.59V threshold, switching 1C out low, Vcap directly plus 24V through the timing resistor keep 1D In- high enough to keep 1D low. In this state, the current flows into 1C out through the 100K summing resistor. This is the only time that the current needs to be restricted. Without this resistor, 1C out low would overcome Vcap and prematurely make 1D out low. We don't want this to occur until the timing capacitor is fully discharged. When 1C out is high, 1D In- is 24V. At the top of the charge cycle, 1C out is 12V and Vcap through the summing diode is 19.89V (20.59 - .7). At that instant, 1C In- will be 19.89V. 1C out low quickly discharges the capacitor through the discharge diode. The lowest point will be 12.7V. At this point, 1D In- will be very nearly 12V. To provide some margin, 1D In+ is fixed at 12.4V. This reference can be shared by all circuits.

As previously explained, 1D out low is lower than the OR node low so that even when the overcurrent is removed (by shutting off the load switches) 2A/1A out will still be high. When both 1C out and Vcap are back down to nearly 12V, 1D out switches high. This voltage must be higher than the OR node low of 12.19V in order to allow 2A/1A out to go low, turning the load switches back on. However, it must be lower than the 23.3V OR node voltage at overcurrent so that the load switches can be immediately turned off. A 50% voltage divider of 47K and 47K to 12V provides 2A/1A In- of 18V when 1D out is high and 12V when 1D out is low. To recap:

Assume that the circuit comes up with one or both 2A and 1A out high, turning off one or both load switches. Assume that neither driver has an overcurrent condition. 2B and 1B outputs are both low and the summing node is low.

Assume that 1C out is low (12V) and Vcap (timing capacitor) is 12.7V. 1C In+ will be 12.19V. 1C out stays low because In+ is lower than In- (with a 0.51V margin). With 1C out = 12V and Vcap = 12.7V, 1D In- will be 12V, which is less than 1D In+ (with a 0.4V margin). Therefore 1D out goes high. 2A and 1A In- see 18V. 2A/1A In+ is 12.19V so 2A/1A out go low (if not already) turning on the load switches.

Assume, instead, that 1C out is initially high (24V). 1C In+ will be 20.59V. 1C can't remain in this state forever because the timing capacitor will charge toward 24V when the discharge diode is reverse biased. However, while 1C out remains high, 1D out is low, presenting 12V to 2A and 1A In-. Since their In+ is 18V, their outputs go high, turning off the load switches. This doesn't change the overcurrent circuit state, because it was assumed that there wasn't overcurrent and, therefore, both 2B and 1B outputs were already low. The circuit would stick in this state except that when Vcap reaches 20.59V, 1C out will go low. This changes 1C In+ to 12.19V, latching 1C in this state, since the discharge diode doesn't permit 1C out low to pull Vcap lower than 12.7V. 1D out remains low even when 1C out goes low because 1D In- is the sum of Vcap and 1C out. When 1C out low discharges the timing capacitor down to approximately 12.7, 1D out goes high (24V). With 2A and 1A In+ now at 18V, their outputs go low, turning on the load switches. At this point, 1C out is low and Vcap is 12.7V, the same condition as previously assumed. This is the steady state no overcurrent condition.

If either 2B or 1B detects overcurrent, the OR node voltage goes to 23.3V. 1C output had been low (12V) and 1C In+ 12.19V. 1C In+ instantaneously goes to 15.6V, causing 1C out to go high, raising In+ still further to 23.78V. With 1C out high, 1D out goes low. 2A/1A In- is now 12V while In+ is 23.3V, causing 2A and 1A out to go high, turning off the load switches. As soon as the load current of the overloaded driver reduces to below the trigger point, the overcurrent comparator OR node returns low. This reduces 1C In+ to 20.59V but 1C out still remains high until Vcap reaches this level. Meanwhile, the load switches remain off. When Vcap reaches 20.59V, 1C out goes low and begins discharging Vcap through the discharge diode. The instantaneous 1D In- voltage at this time is 19.89V and 1D out remains low. 1C out low quickly discharges the timing capacitor to 12.7V whereupon 1D In- becomes 12V and 1D out goes high. This makes 2A/1A In- 18V and 2A/1A out go low, turning the load switches back on. Since 1C out is low and Vcap is 12.7, this is the steady state condition.